为满足集成电路对大尺寸硅片的高品质要求,奕斯伟材料采用先进的工艺及量测设备,通过对量产工艺的不断优化提升,确保产品品质。目前在单晶缺陷控制、几何形貌、颗粒及金属管控等方面均已达到国际先进水平。

奕斯伟材料搭建了涵盖缺陷分析、杂质分析和硅片性质分析的技术研发平台,通过基础研究体系的建设,加深对硅片特性及客户端应用的理解,针对性开展相关品质参数的工艺开发和改善工作,提升硅片品质。

奕斯伟材料组建了模拟、设计和工艺开发的晶体生长研发团队。一方面,优化特性参数的径向/轴向均匀性,完善小尺寸缺陷的评价技术,提升无缺陷晶体的品质。另一方面,针对细分领域产品特点,开发多样化的长晶技术,以满足不同产品的需求。

奕斯伟材料建立了各工序间参数相互影响、相互制约的研究体系,通过对工艺流程及工序配比的优化,持续提升硅片的平坦度和纳米形貌,探索更优的硅片加工工艺流程。

奕斯伟材料分析研究影响外延膜品质的核心部件,通过对核心部件的自主设计与去金属化优化,结合对外延炉气流调控方式的改善,不断提升外延片的几何形貌、金属水平和表面颗粒。

拉晶工序是指通过12英寸晶体生长,将高纯多晶硅原料通过直拉法,外加磁场抑制熔体对流并控制杂质,生长出缺陷可控、杂质含量低、电阻率均匀分布的高品质12英寸单晶硅棒。晶棒生长完成后,会将其滚磨成直径一致的圆柱,再将晶棒截断去头尾,切割成一定长度的硅块,便于后续加工。

成型工序是将拉晶得到的硅锭加工成表面具备一定平坦度,厚度约为800微米的硅片。为满足集成电路制程对硅片表面的要求,硅锭需经过多线切割、倒角、双面研磨等多道表面加工工序,并在各道工序后进行清洗,以去除加工工序在硅片表面造成的机械损伤和沾污。

抛光工序是确保硅片表面平坦度和纳米形貌的核心工序。为了满足集成电路的制程要求,抛光采用纳米尺寸的浆料对硅片表面和边缘进行化学、物理加工,通过多道抛光工序和不同尺寸的浆料进行精细加工,得到纳米级的表面与边缘形貌。

为符合集成电路制程对硅片表面金属、颗粒、有机物的高品质要求,清洗工序对抛光硅片的表面颗粒进行有效去除,确保达到产品品质要求。采用检查极限为ppt(万亿分之一)的表面金属检测仪和能检单位为20纳米以下的颗粒计数器,对硅片表面品质进行管控,确保优秀出货水准。

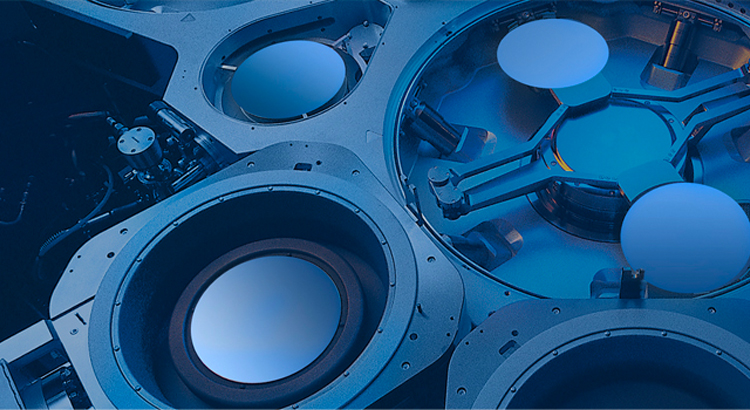

外延工序是以抛光片作为衬底,采用化学气相沉积法(CVD),在硅片表面沉积一层单晶外延层的过程。该工艺采用先进的CVD设备,能够有效控制外延层的电阻率、厚度均匀性、表面品质与边缘形貌。

奕斯伟材料坚持知识产权创新及保护,持续优化专利布局。截至2025年末,已在6个国家和地区、29个技术方向申请1950件专利,并于2024年荣获“第25届中国专利奖优秀奖”、荣获2025年陕西省专利奖一等奖,2025年荣获“国家知识产权示范企业”认证。